# Si-Based Flexible Memristive Systems Constructed Using **Top-Down Methods**

Taeho Moon,<sup>†</sup> Jeongmin Kang,<sup>†</sup> Yong Han,<sup>†</sup> Chunjoong Kim,<sup>‡</sup> Youngin Jeon,<sup>†</sup> Hoyoung Kim,<sup>†</sup> and Sangsig Kim\*,<sup>†</sup>

<sup>+</sup>School of Electrical Engineering, Korea University, Seoul 136-713, Korea

<sup>‡</sup>Lawrence Berkeley National Laboratory, Berkeley, California 94720-8168, United States

Supporting Information

ABSTRACT: Si-based memristive systems consisting of Ag, amorphous Si, and heavily doped p-type Si nanowires were successfully constructed on plastic substrates through top-down methods, including the crystallographic wet etching of Si wafers, transfer onto plastic substrates, and thin film patterning. The memristive systems showed excellent memory characteristics and flexibility, such as intrinsic hysteric and rectifying behaviors, on/off resistance ratios of >1 imes10<sup>5</sup>, and durability for up to 1000 bending cycles. The correlations between the Ag-filament-related nanostructures formed in amorphous

Si and the resistance-switching behaviors were carefully examined with the tunneling current model, transmission electron microscopy, and secondary ion mass spectroscopy to explore the switching mechanism. Our study suggests the promising potential of the Si-based memristive systems for the development of next-generation flexible nonvolatile memory.

KEYWORDS: flexible electronics, nonvolatile memory, memristive system, top-down approach, Si nanowire

# INTRODUCTION

Resistance-switching memories, which are generally referred to as memristive systems or resistance-switching random access memories (RRAMs), have been widely researched as a strong candidate for next-generation nonvolatile memories because of their structural simplicity and excellent memory characteristics.<sup>1-4</sup> Their basic structure is characterized by a very simple layered structure of metal/insulator/metal, which can lead to high scale integration and a low manufacturing cost, through cross-bar-type array. Plastic-substrate-based electronic devices are attractive due to their merits of flexibility, lightweight, and low cost, which can lead to new opportunities in broad areas of commercial electronics. In spite of the rapid progress that has been made in logic gates composed of thin-film transistors on plastic, studies on memristive devices on plastic have rarely been reported to date.5-7

Recently, a few studies on Si-based memristive systems, with the structure of Ag/amorphous Si (a-Si)/heavily doped p-type Si, have been reported by other groups.<sup>8,9</sup> In their studies, Si-based memristive systems were fabricated by two methods, viz. the bottom-up approach using core/shell nanowires and the topdown approach using thin film deposition and patterning. These memristive systems showed peculiar properties compared with general metal-oxide-based systems. First, intrinsic hysteresis was observed without the forming step of high voltage, which can result in high reproducibility and device yield because of the prevention of unpredictable damage. Second, rectifying behavior was observed that was due to their asymmetric electronic structure, which can suppress crosstalk in the array.<sup>2</sup> Despite

these merits, however, it is hard to adopt Si-based memristive systems on plastic through the above two methods. With the bottom-up approach, it is difficult to align the nanowires for large scale integration, whereas with the top-down approach of thinfilm deposition and patterning, it is difficult to acquire highquality crystalline-Si (c-Si) on plastic due to the insufficient thermal and plasma durabilities of plastic. Therefore, to realize Sibased memristive systems on plastic, a new route is required.

A top-down route, consisting of the etching of bulk material and transfer printing is employed in this study to realize Si-based memristive systems on plastic; the top-down route has been continuously developed by J. A. Rogers group.<sup>10,11</sup> This topdown approach looks very attractive for the development of flexible electronics. It can offer excellent controllability over dimension, crystallinity, and doping level for the wide range of materials. Also, it enables the large-scale fabrication of various functional devices on plastic substrates with the precise positioning of prepared materials. Hence, in this research, we demonstrate the Si-based memristive system of Ag/a-Si/heavily doped p-type Si NW on plastic, using Si NWs prepared by the etching of Si wafers and transfer printing. Crossbar switches are designed by Si-NW electrodes and lithographically defined crossed Ag electrodes, and a-Si serves as a switching medium for Ag filaments.

```

Received:

June 28, 2011

Accepted:

September 7, 2011

Published:

September 07, 2011

```

#### EXPERIMENTAL SECTION

Heavily doped Si NWs were formed by the crystallographic wet etching of (100)-oriented *p*-type-Si wafers (B-doping concentration =  $\sim 1 \times 10^{21}$  atoms/cm<sup>3</sup>) using a tetramethylammonium hydroxide (TMAH) solution.<sup>12</sup> The formed Si NWs were transferred onto polyethersulfone (PES) substrates by a direct transfer method.<sup>13</sup> The *a*-Si thin films were sputter-deposited on the Si NWs at room temperature with a thickness of  $\sim 30$  nm. Ag ( $\sim 60$  nm) as a top electrode and Al ( $\sim 60$  nm) as contact pads of the Si NWs were deposited by evaporation at room temperature and patterned by photolithography and lift-off methods. Before the Al deposition, the *a*-Si in the patterned regions was etched by HF solution. (The *a*-Si is etched by HF, but the *c*-Si is not.<sup>14</sup>) Finally, the samples were annealed at 150 °C under an Ar atmosphere to improve their contact properties.

The memristive characteristics were examined using a semiconductor-parameter analyzer (HP4155C, Agilent). Three-terminal measurements with a voltage-measurement unit (VMU) were used to evaluate the junction resistances without the resistances caused by the Si nanowires and Al contact.<sup>8</sup> I-V curves were acquired between -3and 4 V during 100 cycles. Retention tests were performed up to  $1 \times 10^3$  s for on and off states after writing or erasing, respectively, with the reading voltage of 2 V. In the bending tests, the device size was 2 cm  $\times$ 2 cm and the bending radius was fixed at 1.3 cm. The direction of bending was parallel to that of the Si NWs. The fabrication processes of the Si NWs were observed by scanning electron microscopy (SEM: S-4300, Hitachi). The Ag-filament-related nanostructures were investigated with transmission-electron microscopy (TEM: Tecnai F20, FEI) and secondary ion mass spectroscopy (SIMS: IMS 7f, CAMECA).

#### RESULTS AND DISCUSSION

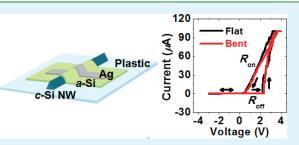

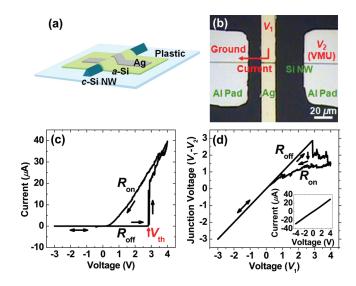

A schematic illustration of a memristive device constructed on a plastic substrate is shown in Figure 1a. Ag and a heavily doped p-type Si NW are used as the electrodes and a-Si is used as a switching medium. Then, a single switch is formed at the junction of Ag/a-Si/Si NW. The Si NWs were formed by the crystallographic wet etching of Si wafers, and the formed Si NWs, exhibiting the triangular crosssection with the base length of  $\sim$ 340 nm, were transferred onto plastic substrates by a direct transfer method<sup>12,13</sup> (see Figure S1 in the Supporting Information). Figure 1b shows the optical image of a representative device fabricated in this study. The current–voltage (I-V) curve was acquired between the Ag electrode  $(V_1)$  and left Al Pad (ground), and the voltage  $(V_2)$  of the right Al pad was continuously measured with a VMU unit to acquire the junction resistance. The voltage difference  $(V_1 - V_2)$  between the Ag electrode and the right Al pad reflects the actual voltage drop by the junction, without the affection by the Si-NW resistance. Figure 1c shows the I-V curve of the typical device, showing the well-defined hysteresis induced by the transitions between the high resistance state and low resistance state; the voltage was swept in the sequence,  $0 V \rightarrow 4 V \rightarrow -3 V \rightarrow 0 V$ . The threshold voltage ( $V_{\rm th}$ ) acquired from several I-V curves was 2.9  $\pm$  0.5 V. Rectification behavior is also observed, without hysteresis in a negative voltage range. This behavior indicates that the Ag ions can easily diffuse away from the Si NW even at small negative voltage and the energy-barrier height for this diffusion is comparable to thermal energy at room temperature.<sup>8</sup> Figure 1d shows the change of the junction voltage  $(V_1 - V_2)$  as a function of the device voltage  $(V_1)$ . The junction resistances were estimated from the measured junction voltage and current. For example, in the case of the on-current of Figure 1c, the device resistance of  $2.1 \times 10^5 \Omega (V_1 = 1 \text{ V})$  is matched with the junction resistance of

Figure 1. (a) Schematic illustration of the memristive device fabricated on a plastic substrate. Ag and Si NW (B-doping concentration =  $\sim 1 \times$  $10^{21}$  cm<sup>-3</sup>) are used for the electrodes, and *a*-Si is used as a switching medium. A single switch is formed at the junction of Ag/a-Si/Si NW. (b) Plan-view image of the fabricated device taken by optical microscopy. Al pads were deposited at both ends of the Si NW. The I-V curve is acquired between the Ag electrode  $(V_1)$  and left Al Pad (ground), and the voltage  $(V_2)$  of the right Al pad is continuously measured with a VMU unit to acquire the junction resistance. (c) AI - V loop obtained from the typical device in the range between -3 and 4 V. It shows well-defined hysteresis with the average-threshold voltage ( $V_{\rm th}$ ) of 2.9  $\pm$  0.5 V. The arrows indicate the voltage-sweep direction. (d) Change of junction voltage  $(V_1 - V_2)$  as a function of device voltage  $(V_1)$ . Because of the potential drop caused by the Si NW and Al contact, the change of the junction voltage, compared with the device voltage, is observed in the on state. The inset shows the linearity of the I-V curve taken from the Si NW (with Al contacts), indicating ohmic behavior.

$1.6 \times 10^5 \Omega (V_1 - V_2 = 0.73 \text{ V})$ . The *I*-*V* curve of the Si NW (with Al contacts) is plotted in the inset of Figure 1d. Its linear shape confirms the ohmic behavior of the device, with a resistance of  $1.4 \times 10^5 \Omega$ . Therefore, the value of the acquired junction resistance is reasonable, considering the Si-NW resistance and device geometry shown in Figure 1b.

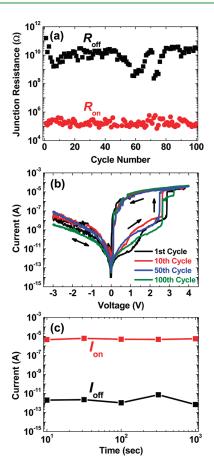

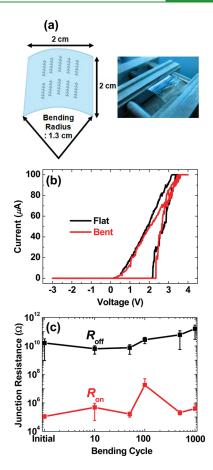

During cycling, the change of the on/off junction resistances (acquired at a device voltage of 1 V) is shown in Figure 2a. The on/off resistance ratio is well maintained at  $>10^5$  for up to 100 cycles. The corresponding I-V curves at the first, 10th, 50th, and 100th cycles are shown in Figure 2b. The curve shapes are wellmaintained during cycling, although the off-current and set voltage vary slightly according to the progress of cycling, which is likely due to the structural modification of the *a*-Si matrix and/ or the change of the Ag-diffusion kinetics. Retention tests were performed after the device was written on or off (Figure 2c). Little changes in current levels are observed up to  $1 \times 10^3$  s, which confirms the nonvolatile nature of the fabricated device. To evaluate the flexibility of the device, we performed bending tests. Figure 3a shows a schematic illustration of the device fabricated on plastic with bending curvature (left) and a photograph of the bent device prior to the measurements (right). The shapes of the I-V curves in the flat and bent states are similar, as shown in Figure 3b. The bending durability was also tested by observing the changes of the on/off junction resistances during bending cycling. (One bending cycle means that the device is

**Figure 2.** (a) Change in the on/off junction resistance (acquired at a device voltage of 1 V) during cycling. The on/off resistance ratio is well maintained at >1 × 10<sup>5</sup> for up to 100 cycles. (b) Corresponding I-V curves at the first, 10th, 50th, and 100th cycles. The curve shapes are well maintained during cycling, although the off current and set voltage change slightly according to the progress of cycling, which may be due to the structural modification of the *a*-Si matrix and/or the change of the Ag-diffusion kinetics. (c) Retention-test results for on and off states up to  $1 \times 10^3$  s, confirming the nonvolatile nature of the fabricated device.

returned to the flat state after bending with a fixed curvature.) The durability test confirmed that the performance was well maintained for up to 1000 bending cycles, as shown in Figure 3c. The maintenance of the performance is probably due to the short vertical channel of nanometer scale and the ductility of the materials.<sup>6</sup>

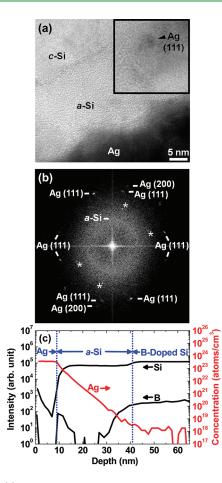

The Ag-filament-related nanostructures were examined with TEM, SIMS, and the tunneling-current model to explore the switching mechanism. The TEM image reveals that the interface between Ag and a-Si is not sharp and Ag is nonuniformly included in the a-Si matrix (Figure 4a). The inset of Figure 4a is the magnified image of the Ag-included region in the a-Si layer. The image shows that the Ag nanocrystal, with the lattice image of (111) planes, is embedded in the a-Si layer. Figure 4b is the Fourier-transformed diffraction pattern of the Ag-included region, confirming the presence of Ag-metallic phase with (111) and (200) spots and a-Si phase with halo ring patterns. The Ag–Si system is a simple eutectic in the phase diagram and, therefore, Ag<sub>x</sub>Si<sub>y</sub> alloys do not exist thermodynamically.<sup>15</sup> (The spots with asterisk marks are assigned to crystalline SiO<sub>2</sub>, probably due to the damage caused by local heating during the

**Figure 3.** (a) Schematic illustration of the device fabricated on plastic with bending curvature (left), and photograph of the bent device with a size of 2 cm  $\times$  2 cm prior to the measurements (right). The bending radius was fixed at 1.3 cm, and the direction of bending was parallel to that of the Si NW. (b) I-V curves between flat and bent states, with a compliance current of 100  $\mu$ A, showing that the device performances are similar. (c) The change in the junction resistance as a function of bending cycles. One bending cycle means that the device is returned to the flat state after bending with a fixed curvature. The performance is well maintained for up to 1000 bending cycles.

TEM-sample preparation.) SIMS-depth profiles were acquired with the samples fabricated on planar Si wafers (Figure 4c). Strikingly, a fully diffused Ag profile into the *a*-Si matrix is observed, probably due to Ag diffusion during deposition. The Ag profiles of the samples with and without postannealing at 150 °C were similar, as shown in Figure S2 in the Supporting Information. It is questionable how this diffusion profile was made. With the Ag-diffusivity (*D*) in *a*-Si, expected to be  $\sim 1 \times 10^{-29}$  cm<sup>2</sup>/s at room temperature, the time (*t*) required for 30-nm diffusion (*L*) is estimated to be  $\sim 1 \times 10^{18}$  s by the equation,  $L \approx (Dt)^{1/2.16}$  Therefore, it is thought that this abnormal diffusion profile may be related to the impurity-mediated enhanced diffusion caused by unavoidable contamination and/or the defect structure of *a*-Si.<sup>17,18</sup> Detailed studies are needed to clarify Ag-diffusion kinetics and thereby correlate it with the switching behavior.

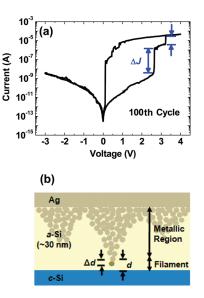

The off-currents obtained from the I-V curves were analyzed by a tunneling-current model. Figure 5a represents the I-Vcurve of the device at the 100th cycle, as shown in Figure 2b. Two current-jumping steps are clearly observed at ~2.6 and ~3.2 V,

**Figure 4.** (a) Cross-section TEM image, showing the interfaces of the Ag/*a*-Si/*c*-Si structure. The inset is the magnified image of the Ag-included region in the *a*-Si layer. (b) Fourier-transformed diffraction pattern of the Ag-included region. (c) SIMS-depth profile of the sample whose structure is Ag/*a*-Si ( $\sim$ 30 nm)/planar B-doped Si wafer.

and this stepwise increase in current magnitude may indicate that the switching is due to a single filament instead of multiple filaments.<sup>19</sup> Simply, the tunneling current depends on the tunneling distance, assuming that the barrier height is constant. Therefore, the change of the tunneling distance at the jumping steps can be calculated by the equation,

$$\Delta J = \frac{J(\text{afterjump})}{J(\text{beforejump})} = e^{(\sqrt{2m^* \Delta E}/\hbar) 2\Delta d}$$

where  $\Delta J$  is the change of the tunneling-current density,  $m^*$  is the electron-effective mass in *a*-Si (0.09  $m_0$ ),  $\Delta E$  is the barrier height ( $\Phi_{Ag} - X_{Si} = 0.31 \text{ eV}$ ),  $\hbar$  is Plank's constant, and  $\Delta d$  is the change of the tunneling distance.<sup>9,20,21</sup> The estimated tunneling-distance changes are 2.7 nm (2.6 V) and 0.8 nm (3.2 V), and thereby the total filament length (d) is approximately 3.5 nm. Actually, not all of the curves showed clear jumping steps, such as those in Figure 5a. Nevertheless, the filament length, which is of the order of several nanometers (obtained using the calculations from several I-V curves) was unchanged. On the basis of these nanostructural analyses, a schematic model is drawn to explain the switching mechanism of our memristive systems (Figure 5b).<sup>9,22</sup> Intrinsically, a nonuniform Ag diffusion profile into the *a*-Si matrix is observed after the fabrication process. At certain positions, the Ag filament is connected and disconnected

**Figure 5.** (a) I-V curve obtained from the device at the 100th cycle, clearly showing two current-jumping steps in the off-current region. The changes in the tunneling distance  $(\Delta d)$  at each jumping step can be simply calculated from the change in the tunneling current  $(\Delta J)$ , assuming that the barrier height is constant. The total filament length (d) can then be estimated. (b) Schematic model related to the Ag filaments, assuming that the *c*-Si electrode is of the planar type.

according to the bias conditions, due to electromigration, and the Ag profile is continuously rearranged during cycling, resulting in the structural modification of the *a*-Si. Most of the 30-nm-thick *a*-Si is metallic, because of Ag inclusion, and the filament with a length of several nanometers controls the device performance.

### CONCLUSIONS

In summary, Si-based memristive devices were successfully constructed on plastic through our new top-down route. The devices showed excellent memory characteristics and flexibility, such as intrinsic hysteric and rectifying behaviors, on/off resistance ratio of >1  $\times$  10<sup>5</sup>, retention time of > 1  $\times$  10<sup>3</sup> s, and durability for up to 1000 bending cycles. The Ag-filament-related nanostructures were carefully analyzed to explore the switching mechanism by TEM, SIMS, and the tunneling-current model. It is suggested that the Ag nanocrystals, embedded in the a-Si layer during the fabrication process, act as an electrical path, and this nanostructure is well matched with the intrinsic resistanceswitching behavior. The nonuniform Ag profile is continuously changed according to the bias conditions, and Ag electromigration, in the region of several nanometers only, determines the device performance. These results can help us to gain an understanding about the correlation among the nanostructure, memory/switching mechanism, and device performance for various memristive systems. Furthermore, our study suggests the promising potential of Si-based memristive systems as future flexible nonvolatile memory devices.

## ASSOCIATED CONTENT

**Supporting Information.** Details about Si-NW fabrication and SIMS-depth profile of the as-deposited sample. This material is available free of charge via the Internet at http://pubs.acs.org/.

## AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: sangsig@korea.ac.kr.

# ACKNOWLEDGMENT

This work was supported by the IT R&D program of MKE/ KEIT (10030559, Development of next-generation high-performance organic/nano materials and printing process technology), the Nano R&D Program (M10703000980-08M0300-98010), the World Class University Project (WCU, R32-2008-000-10082-0) of the Ministry of Education, Science, and Technology (Korea Science and Engineering Foundation), Seoul R&BD Program (PA090914), and the Hynix-Korea University Nano-Semiconductor Program.

### REFERENCES

- (1) Chua, L. O. IEEE Trans. Circuit Theory 1971, 18, 507.

- (2) Scott, J. C. Science 2004, 304, 62.

- (3) Waser, R.; Aono, M. Nat. Mater. 2007, 6, 833.

- (4) Nagashima, K.; Yanagida, T.; Oka, K.; Taniguchi, M.; Kawai, T.; Kim, J.-S.; Park, B. H. *Nano Lett.* **2010**, *10*, 1359.

- (5) Yun, J.; Cho, K.; Park, B.; Park, B. H.; Kim, S. J. Mater. Chem. 2009, 19, 2082.

- (6) Cheng, C.-H.; Yeh, F.-S.; Chin, A. Adv. Mater. 2011, 23, 902.

- (7) G.-Hackett, N.; Hamadani, B.; Dunlap, B.; Suehle, J.; Richter, C.;

- Hacker, C.; Gundlach, D. *IEEE Electron Device Lett.* 2009, 30, 706.

(8) Dong, Y.; Yu, G.; McAlpine, M. C.; Lu, W.; Lieber, C. M. *Nano Lett.* 2008, 8, 386.

- (9) Jo, S. H.; Kim, K.-H.; Lu, W. Nano Lett. 2009, 9, 870.

(10) Mack, S.; Meitl, M. A.; Baca, A. J.; Zhu, Z.-T.; Rogers, J. A. Appl. Phys. Lett. **2006**, 88, 213101.

(11) Baca, A. J.; Meitl, M. A.; Ko, H. C.; Mack, S.; Kim, H.-S.; Dong, J.; Ferreira, P. M.; Rogers, J. A. *Adv. Funct. Mater.* **2007**, *17*, 3051.

- (12) Lee, M.; Koo, J.; Chung, E.-A.; Jeong, D.-Y.; Koo, Y.-S.; Kim, S. Nanotechnology **2009**, 20, 455201.

- (13) Chung, E.-A.; Koo, J.; Lee, M.; Jeong, D.-Y.; Kim, S. Small 2009, 5, 1821.

(14) O'Mara, W. C.; Haber, R. B.; Hunt, L. P. *Handbook of Semiconductor Silicon Technology*; William Andrew Publishing: Burlington, VT, 1990.

(15) Olesinski, R. W.; Gokhale, A. B.; Abbaschian, G. J. Bull. Alloy Phase Diagrams **1989**, *10*, 635.

(16) Coffa, S.; Poate, J. M.; Jacobson, D. C.; Frank, W.; Gustin, W. *Phys. Rev. B* **1992**, *45*, 8355.

(17) Rollert, F.; Stolwijk, N. A.; Mehrer, H. J. Phys. D: Appl. Phys. 1987, 20, 1148.

(18) McBrayer, J. D.; Swanson, R. M.; Sigmon, T. W.; Bravman, J. Appl. Phys. Lett. **1983**, 43, 653.

(19) Jo, S. H.; Kim, K.-H.; Lu, W. Nano Lett. 2009, 9, 496.

(20) Shannon, J. M.; Nieuwesteeg, K. J. B. M. Appl. Phys. Lett. 1993, 62, 1815.

(21) Michaelson, H. B. J. Appl. Phys. 1977, 48, 4729.

(22) Jo, S. H.; Chang, T.; Ebong, I.; Bhadviya, B. B.; Mazumder, P.; Lu, W. Nano Lett. **2010**, *10*, 1297.